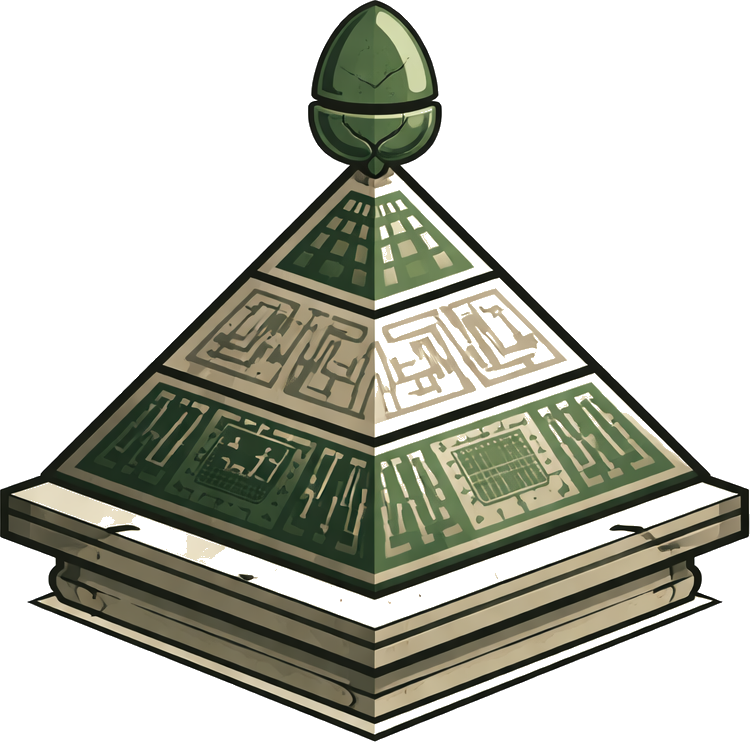

Acorn Econet Bridge Variant 1 Memory Map

Addresses outside the ROM used by Acorn Econet Bridge Variant 1 at run time — zero-page

workspace, RAM buffers, and memory-mapped I/O. For the code that lives

at &E000 upward, see the disassembly

listing.

Zero page

| Address | Name | Access | Description |

|---|---|---|---|

&0000 |

st_ptr_lo |

R/W | Low byte of the self-test scan pointer.

Paired with Also used as an anti-aliasing tripwire byte (the |

&0001 |

st_ptr_hi |

R/W | High byte of the self-test scan pointer.

Paired with Also a scratch victim byte during |

&0002 |

st_page_count |

R/W | Page counter for the self-test scans.

Pre-loaded with a hard-coded Also a scratch victim byte during |

&0003 |

st_pass_phase |

R/W | Self-test pass-phase flag.

Initialised by |

&0080 |

mem_ptr_lo |

R/W | Low byte of the indirect pointer.

Paired with Used by |

&0081 |

mem_ptr_hi |

R/W | High byte of the indirect pointer.

Paired with |

&0082 |

top_ram_page |

R/W | Highest page that verified |

RAM workspace

| Address | Name | Access | Description |

|---|---|---|---|

&0200 |

tx_end_lo |

R/W | Low byte of the TX end-pointer, consumed by |

&0201 |

tx_end_hi |

R/W | High byte of the TX end-pointer.

Paired with |

&0214 |

ctr24_lo |

R/W | Low byte of a 24-bit counter reused by several routines.

|

&0215 |

ctr24_mid |

R/W | Middle byte of the 24-bit counter.

Rooted at |

&0216 |

ctr24_hi |

R/W | High byte of the 24-bit counter.

Rooted at |

&0228 |

rx_len |

R/W | Byte count received into the RX frame buffer. Written by the drain loop once the ADLC reports end-of-frame; read back by the dispatch paths to decide how many payload bytes to process. |

&0229 |

announce_flag |

R/W | Event-driven re-announcement selector. Set by Polled by |

&022A |

announce_tmr_lo |

R/W | Low byte of the 16-bit re-announcement countdown.

Decremented every pass through |

&022B |

announce_tmr_hi |

R/W | High byte of the 16-bit re-announcement countdown.

Paired with |

&022C |

announce_count |

R/W | Remaining |

RAM buffers

| Address | Name | Access | Description |

|---|---|---|---|

&023C |

rx_dst_stn |

R/W | RX frame buffer byte 0 – destination station number.

First byte of the 20-byte RX staging area at |

&023D |

rx_dst_net |

R/W | RX frame buffer byte 1 – destination network number. |

&023E |

rx_src_stn |

R/W | RX frame buffer byte 2 – source station number. |

&023F |

rx_src_net |

R/W | RX frame buffer byte 3 – source network number. |

&0240 |

rx_ctrl |

R/W | RX frame buffer byte 4 – control byte.

Bridge protocol uses |

&0241 |

rx_port |

R/W | RX frame buffer byte 5 – port number.

The bridge-protocol port is |

&0248 |

rx_query_port |

R/W | RX frame buffer byte 12 – port on which the querier wants the bridge to send its response. |

&0249 |

rx_query_net |

R/W | RX frame buffer byte 13 – network number that a |

&025A–&0359 |

reachable_via_b |

R/W | 256-byte routing table for forwarding out of side B. Indexed by destination network number; a non-zero entry means "this network is reachable from here". Consulted by |

&035A–&0459 |

reachable_via_a |

R/W | 256-byte routing table for forwarding out of side A. Indexed by destination network number; a non-zero entry means "this network is reachable from here". Consulted by |

&045A |

tx_dst_stn |

R/W | TX frame buffer byte 0 – destination station number.

First byte of the outbound frame staging area at |

&045B |

tx_dst_net |

R/W | TX frame buffer byte 1 – destination network number. |

&045C |

tx_src_stn |

R/W | TX frame buffer byte 2 – source station number. |

&045D |

tx_src_net |

R/W | TX frame buffer byte 3 – source network number. |

&045E |

tx_ctrl |

R/W | TX frame buffer byte 4 – control byte in a scout frame, or the first data byte in a data frame. The same buffer serves both frame types; the caller chooses the semantics. |

&045F |

tx_port |

R/W | TX frame buffer byte 5 – port in a scout frame, or the second data byte in a data frame.

Pair with |

&0460 |

tx_data0 |

R/W | TX frame buffer byte 6 – first optional scout payload byte.

For example, a queried network number in a |

I/O — side A

| Address | Name | Access | Description |

|---|---|---|---|

&C000 |

net_num_a |

R | Econet side A network number, read at The Bridge has no station number of its own – it sits on each Econet segment as a promiscuous receiver and broadcaster. |

&C800 |

adlc_a_cr1 |

R/W | ADLC A control/status port 0. Write: CR1 (or CR3 when AC=1 in CR1). Read: SR1. IRQ summary is in SR1 bit 7; |

&C801 |

adlc_a_cr2 |

R/W | ADLC A control/status port 1. Write: CR2 (or CR4 when AC=1). Read: SR2. |

&C802 |

adlc_a_tx |

R/W | ADLC A TX/RX FIFO port. Write: push a byte into the TX FIFO (frame continues). Read: pop a byte from the RX FIFO. |

&C803 |

adlc_a_tx2 |

W | ADLC A TX-last-byte port. Write: push the final byte of a frame (chip closes the frame and appends the FCS + flag). Reading this port is not used by the Bridge. |

I/O — side B

| Address | Name | Access | Description |

|---|---|---|---|

&D000 |

net_num_b |

R | Econet side B network number, read at Paired with |

&D800 |

adlc_b_cr1 |

R/W | ADLC B control/status port 0. Write: CR1 (or CR3 when AC=1 in CR1). Read: SR1. IRQ summary is in SR1 bit 7; CR3 bit 7 (reached via this port with AC=1) drives IC18's |

&D801 |

adlc_b_cr2 |

R/W | ADLC B control/status port 1. Write: CR2 (or CR4 when AC=1). Read: SR2. |

&D802 |

adlc_b_tx |

R/W | ADLC B TX/RX FIFO port. Write: push a byte into the TX FIFO (frame continues). Read: pop a byte from the RX FIFO. |

&D803 |

adlc_b_tx2 |

W | ADLC B TX-last-byte port. Write: push the final byte of a frame (chip closes the frame and appends the FCS + flag). Reading this port is not used by the Bridge. |